新規サイト002のヘッダー

趣味でHP(嘘は付いてないけど間違いはある必ず裏をとってね)

解説書ではありません。Verilogは既に出来るがちょっと細かいところ忘れた時に見る例文。繰り返し部分は省略してるので端子名は合っていない筈。

Verilogメモ

◆Verilogの細かい記述忘れた時のメモ◆

_/_/_/_/_/_/_/_/_/_/_/_/_/_/_/_/_/_/_/_/_/_/_/_/_/_/_/

■回路記述

_/_/_/_/_/_/_/_/_/_/_/_/_/_/_/_/_/_/_/_/_/_/_/_/_/_/_/

●親モジュール

// ------------------------------

// Circuit 回路名

// ------------------------------

//

// Modify contents

// Version 07 Level 01 Date:04.08.2008

//

`timescale 1ns/1ns

module UCLTOP01_04 (

usbac_same,

ck_500u_vref ,

uvlo_vref ,

ctl_chg ,

uvlo_bat_d ,

//----------<省略>-----------------------------

i2c_f1h_d07 , // For test mode ( Go to 30min time over )

i2c_f1h_d06 , // For test mode ( Go to TTC time over )

i2c_f1h_d01 // For test mode ( Short time mode )

) ;

input usbac_same ; // D15 and D14 change in same time.

//----------<省略>-----------------------------

input ck_500u_vref ; // Clock

input uvlo_vref ; // 0:Reset

output ctl_stat ; // LED ( Show charging )

//----------<省略>-----------------------------

output test_stat_tm ; // Test mode ( For each timer )

output ctl_oscchg ; // H:Demand clock

// ---------------------------

// For h-level output

// ---------------------------

wire l_err_vbovp_d ; //

wire ck_500u_vref_inbuff ;

// 組み合わせ回路

assign l_err_vbovp_d = bs491 ; // Insert H-type buffer

UIN_PORT01_01 UIN_PORT01_01_U001(

.ck_500u_vref(ck_500u_vref_inbuff) , // Clock

//----------<省略>-----------------------------

.OUT(m_stop) , // Noise cuted H signa

.ctl_osc(ctl_osc_xchge) // H:Demand clock

) ;

UTEST_INPUT_01 UTEST_INPUT_01_U1(

.test_mode(test_mode),

//----------<省略>-----------------------------

.err_vbovp_inbuff_t(err_vbovp_inbuff_t) , // Output (Selected input)

.bs491(bs491) , // Degrich output

.test_5_out(test_5_out) // Output (Pule from in and out)

) ;

UIN_PORT_L60_01 UIN_PORT_L60_01_U006(

.test_short(i2c_f1h_d01_inbuff), // Short time mode

//----------<省略>-----------------------------

.ck_500u_vref(ck_500u_vref_inbuff) , // Clock

.x_reset(x_reset) , // Reset

.IN(xdet_taper_t) , // Pure input

.OUT(taper_100ma) , // Noise cuted H signa

.ctl_osc(ctl_osc_taper) // H:Demand clock

) ;

// 一行で書く

ACTIVE_TS ACTIVE_TS_U1(.state(state),.pre_err_ts_inbuff(pre_err_ts_inbuff),.err_ts_inbuff(err_ts_inbuff));

// 呼び素子空呼び出し

UYOBI01_01 YOBI_U1 () ;

UYOBI02_01 YOBI_U2 () ;

UYOBI03_01 YOBI_U3 () ;

endmodule

module ACTIVE_TS(state,pre_err_ts_inbuff,err_ts_inbuff );

input [32:0] state ;

input pre_err_ts_inbuff ;

output err_ts_inbuff ;

wire pre2_err_ts_inbuff ;

// ゲート記述

ND1LU1 ADD1430A ( .A(pre2_err_ts_inbuff) , .X(mid_A14000) );

ND1LU1 ADD1430E ( .A(mid4_A14000) , .X(mid5_A14000) );

RT2LU1 ADD1430Y ( .A1(mid5_A14000) , .A2(pre2_err_ts_inbuff) , .X(err_ts_inbuff) );

// ビット指定の組み合わせ回路

assign pre2_err_ts_inbuff = pre_err_ts_inbuff &

( state[3] |

state[31] |

state[32] |

state[12] );

endmodule

●アサイン文(論理合成でバッファーを発生させる、又は手挿入)

module UOUTBUFF_002 (

out_int,

out

);

output out ;

input out_int ;

assign out = out_int ;

endmodule

●オールウェイズ文の中でケースを使用、SIM様遅延、合成用パラメータ、ビット演算子

// synopsys async_set_reset "x_reset"

always @( posedge total_trigger or negedge x_reset ) begin

if( x_reset == 1'b0 ) begin

#3 state[32:0] <= 33'b000_00000_00000_00000_00000_00000_00001 ;

flag_30min <= 1'b0 ;

flag_ttc <= 1'b0 ;

recharge <= 1'b0 ;

charge_again <= 1'b0 ;

flag_uvlo_bat <= 1'b0 ;

end

else begin

casex({become_33 ,become_32 ,become_31 ,become_30 ,become_29 ,become_28 ,become_27 ,

become_26 ,become_25 ,become_24 ,become_23 ,become_22 ,become_21 ,become_20 ,

become_19 ,become_18 ,become_17 ,become_16 ,become_15 ,become_14 ,become_13 ,

become_12 ,become_11 ,become_10 ,become_09 ,become_08 ,become_07 ,become_06 ,

become_05 ,become_04 ,become_03 ,become_02 ,become_01}) //synopsys parallel_case

33'bxxx_xxxxx_xxxxx_xxxxx_xxxxx_xxxxx_xxxx1 :

begin

#3 state[32:0] <= 33'b000_00000_00000_00000_00000_00000_00001 ;

recharge <= 1'b0 ;

charge_again <= 1'b0 ;

end

//----------<省略>-----------------------------

33'bxxx_xxxxx_xxxxx_xxxx1_xxxxx_xxxxx_xxxxx :

begin

#3 state[32:0] <= 33'b000_00000_00000_00001_00000_00000_00000 ;

flag_30min <= 1'b0 ;

flag_ttc <= 1'b0 ;

recharge <= 1'b0 ;

charge_again<= 1'b0 ;

end

33'bxxx_xxxxx_xxxxx_xxx1x_xxxxx_xxxxx_xxxxx :

begin

#3 state[32:0] <= 33'b000_00000_00000_00010_00000_00000_00000 ;

end

//----------<省略>-----------------------------

33'bx1x_xxxxx_xxxxx_xxxxx_xxxxx_xxxxx_xxxxx :

begin

#3 state[32:0] <= 33'b010_00000_00000_00000_00000_00000_00000 ;

end

33'b1xx_xxxxx_xxxxx_xxxxx_xxxxx_xxxxx_xxxxx :

begin

#3 state[32:0] <= 33'b100_00000_00000_00000_00000_00000_00000 ;

end

default #3 state[32:0] <= 33'b000_00000_00000_00000_00000_00000_00001 ;

endcase

end// if's end

end//always's end

_/_/_/_/_/_/_/_/_/_/_/_/_/_/_/_/_/_/_/_/_/_/_/_/_/

■シミュレーション記述

_/_/_/_/_/_/_/_/_/_/_/_/_/_/_/_/_/_/_/_/_/_/_/_/_/

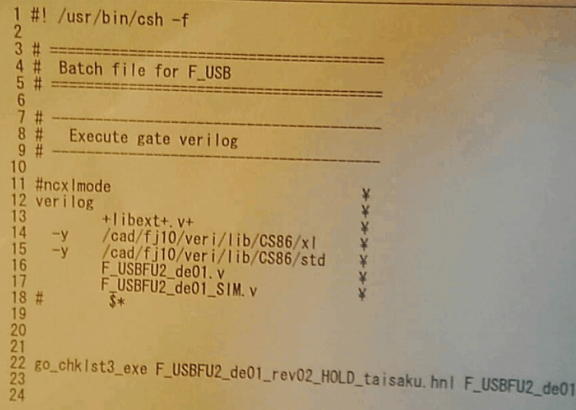

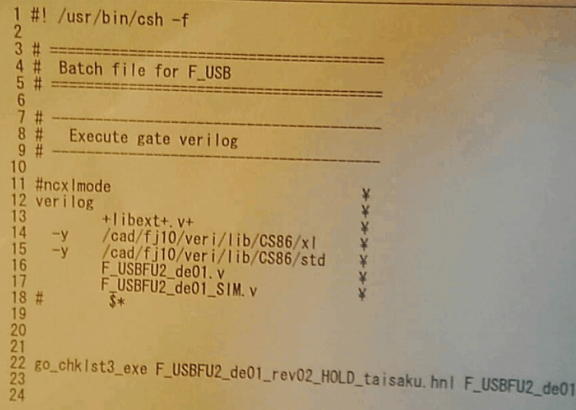

●ゲートSIM起動

●NC-Verilog起動

・リストで指定

#!/bin/csh -f

rm -rf INCA_libs

ncverilog -f vlist +access+wr

・回路名指定

#!/bin/csh -f

#rm -rf INCA_libs

ncverilog SIM_UCCVSD_REGWATCH_01.v UCCVSD_REGWATCH_01.v +access+wr

# +libext+.v+ \

# -y /home/assplib/CS60ALE/V0.1/logic/veri/xl \

# -y /home/assplib/CS60ALE/V0.1/logic/veri/std \

●トップ(SIMは入出力がない)

// ---------------------------------

//

// Top hierarchy module for test

// Jun.16.2006 Ver 0.01

//

// ---------------------------------

module RTC_SIM;

// R-bus

reg [15:0] RBIN ;

wire [15:0] RBOUT;

reg [1:0] BS ;

reg RBW ;

// パラメータ指定

parameter CLK27MHZ = 20; // About half of 40ns

// 回路呼び出し

RTC_TOP RTC_TOP(

.RBIN(RBIN),

.RBOUT(RBOUT),

.BS(BS),

.RBW(RBW),

);

// -------------

// SELECT 1 BUX

// -------------

initial begin

TEST <= 1'b0;

end

// タスク機能のみ呼び出し

reset;

// タスク直値引渡し呼び出し

rbwrite(16'h04EA,8'hFF);

rbread (16'h04EA);

endmodule

●インクルード

`timescale 1ns/10ps

module SIM_U3DUTYB4_001 ;

`include "../test_common/common.psl"

initial

begin

{b3,b2,b1,b0} = 4'b1001;

#(HALF_CLK*100)

$finish;

end

endmodule

●パラメータ設定

parameter HALF_CLK = 500 ;

●宣言

reg clk;

reg res;

reg b3;

reg b2;

reg b1;

reg b0;

●初期設定

initial

begin

#0clk = 1'b0 ;

#0res = 1'b0 ;

end

●モジュール呼び出し .子(親)

U3DUTYB4_004 X1 (

.b3(b3),

.b2(b2),

.b1(b1),

.b0(b0),

.clk(clk),

.res(res),

.out(out)

);

●クロックとリセットの発生

always #(HALF_CLK)

clk = ~clk ;

initial

begin

res = 1'b0;

@(posedge clk);

@(posedge clk);

#(HALF_CLK/2);

res = 1'b1;

end

●タスクの定義

task yobi_on ;

begin

#(clk_cycle*2*16*300)CTL_CDD1 = 1'b1 ;

if ( i2c_04h_old >= i2c_04h )

check_dac = 1'b0 ;

if ( i2c_04h_old < i2c_04h )

check_dac = 1'b1 ;

#(clk_cycle*2*16*900)CTL_CDD1 = 1'b0 ;

i2c_04h_old = i2c_04h ;

end

endtask

●ファイル出力(起動時)

initial

begin

$dumpfile(create_vcd);

// 0: all node 1: top node

$dumpvars(1, CTL, CK_IN, I2C_04H_D15, I2C_04H_D14, I2C_04H_D13,

I2C_04H_D12, I2C_05H_D15, CTL_CHGSEL, CTL_CDD1, CTL_CDD2,

CS_FINISH, B7, B6, B5, B4, B3, B2, B1, B0 );

end

●スイッチON/OFFで波形出力や遅延解析

initial

begin

//wave file create

`ifdef not_anno

$shm_open(wave_file);

$shm_probe("AS");

`endif

//monitor output

// mon = $fopen(fmon_file) ;

//display output

// dis = $fopen(fdis_file) ;

`ifdef sdf_anno

$shm_open(wave_file_anno); //annotation wave file

$shm_probe("AS");

$sdf_annotate(annotate_file,SIM_U3DUTYB4_001.X1); //set annotation

`endif

//annotate file

// $sdf_annotate(annotate_file,i2c_test.X1.I598); //set annotation

// $sdf_annotate("spx_top.sdf",test_spx_chip_top,,"sdf.log",,"0.6:1.0:1.65",);

end

●データをファイルへ出力

integer fw;

initial

fw = $fopen("temp.ftd");

always @( posedge SIM_U3DUTYB4_001.X1.clk)begin

if(SIM_U3DUTYB4_001.X1.out == 1'b1)

$fdisplay(fw,"P%b%b%b%b%bH",

SIM_U3DUTYB4_001.X1.res,

SIM_U3DUTYB4_001.X1.b3,

SIM_U3DUTYB4_001.X1.b2,

SIM_U3DUTYB4_001.X1.b1,

SIM_U3DUTYB4_001.X1.b0

);

else

$fdisplay(fw,"P%b%b%b%b%bL",

SIM_U3DUTYB4_001.X1.res,

SIM_U3DUTYB4_001.X1.b3,

SIM_U3DUTYB4_001.X1.b2,

SIM_U3DUTYB4_001.X1.b1,

SIM_U3DUTYB4_001.X1.b0

);

end

●簡単に通し,for文、リピート文、各ファイル出力

`timescale 1ns/1ns

module SIM_UDCOUTOP_001 ();

wire [7:0] UDOUT ;

reg [7:0] UDIN ;

// ---------------<省略>-----------------------------------

reg CLK50U;

reg RESET ;

integer temp ;

initial CLK50U = 1'b0;

always #50 CLK50U = ~CLK50U ;

initial begin

RESET = 1'b1 ;

@(posedge CLK50U);

RESET = 1'b0 ;

// for 文

for(temp=255 ; temp >=0 ; temp = temp - 1 )begin

UDIN = temp;

// リピート文

repeat(300) @(posedge CLK50U);

if( UDIN == UDOUT ) $display ("%h=OK",temp); else $display ("%h=NG",temp);

UDIN = 255 - temp;

repeat(300) @(posedge CLK50U);

if( UDIN == UDOUT ) $display ("%h=OK",255-temp); else $display ("%h=NG",255-temp);

end

UDIN = 8'h00;

repeat(256) @(posedge CLK50U);

$finish;

end

//initial #100000 $finish;

UDCOUTOP_001 UDCOUTOP_001(

.UDOUT7(UDOUT[7]),

.UDOUT6(UDOUT[6]),

// ---------------<省略>-----------------------------------

.UDIN1(UDIN[1]),

.UDIN0(UDIN[0]),

.RESET(RESET),

.CLK50U(CLK50U)

);

// ----------

// Make wave

// ----------

initial begin

// For signal scan

//$recordfile("UDCOUTOP_001","sequence");

//$recordvars("trace") ;

//$recordvars("primitives", "drivers") ;

// For IRUN , nc-verilog etc

$shm_open ("UDCOUTOP_001.shm") ;

$shm_probe ( UDCOUTOP_001 , "AS" ) ;

// For vcd

//$dumpvars (1,UDCOUTOP_001) ;

//$dumpfile ("1_1_1.vcd") ;

// For evcd

// $dumpports( UDCOUTOP_001_gate.UDCOUTOP_001,"1_1_1.evcd");

//$dumpports( UDCOUTOP_001,"1_1_1.evcd");

end

initial begin

$sdf_annotate("UDCOUTOP_001.sdf",SIM_UDCOUTOP_001.UDCOUTOP_001); //set annotation

end

endmodule

◆Verilogの細かい記述忘れた時のメモ◆

_/_/_/_/_/_/_/_/_/_/_/_/_/_/_/_/_/_/_/_/_/_/_/_/_/_/_/

■回路記述

_/_/_/_/_/_/_/_/_/_/_/_/_/_/_/_/_/_/_/_/_/_/_/_/_/_/_/

●親モジュール

// ------------------------------

// Circuit 回路名

// ------------------------------

//

// Modify contents

// Version 07 Level 01 Date:04.08.2008

//

`timescale 1ns/1ns

module UCLTOP01_04 (

usbac_same,

ck_500u_vref ,

uvlo_vref ,

ctl_chg ,

uvlo_bat_d ,

//----------<省略>-----------------------------

i2c_f1h_d07 , // For test mode ( Go to 30min time over )

i2c_f1h_d06 , // For test mode ( Go to TTC time over )

i2c_f1h_d01 // For test mode ( Short time mode )

) ;

input usbac_same ; // D15 and D14 change in same time.

//----------<省略>-----------------------------

input ck_500u_vref ; // Clock

input uvlo_vref ; // 0:Reset

output ctl_stat ; // LED ( Show charging )

//----------<省略>-----------------------------

output test_stat_tm ; // Test mode ( For each timer )

output ctl_oscchg ; // H:Demand clock

// ---------------------------

// For h-level output

// ---------------------------

wire l_err_vbovp_d ; //

wire ck_500u_vref_inbuff ;

// 組み合わせ回路

assign l_err_vbovp_d = bs491 ; // Insert H-type buffer

UIN_PORT01_01 UIN_PORT01_01_U001(

.ck_500u_vref(ck_500u_vref_inbuff) , // Clock

//----------<省略>-----------------------------

.OUT(m_stop) , // Noise cuted H signa

.ctl_osc(ctl_osc_xchge) // H:Demand clock

) ;

UTEST_INPUT_01 UTEST_INPUT_01_U1(

.test_mode(test_mode),

//----------<省略>-----------------------------

.err_vbovp_inbuff_t(err_vbovp_inbuff_t) , // Output (Selected input)

.bs491(bs491) , // Degrich output

.test_5_out(test_5_out) // Output (Pule from in and out)

) ;

UIN_PORT_L60_01 UIN_PORT_L60_01_U006(

.test_short(i2c_f1h_d01_inbuff), // Short time mode

//----------<省略>-----------------------------

.ck_500u_vref(ck_500u_vref_inbuff) , // Clock

.x_reset(x_reset) , // Reset

.IN(xdet_taper_t) , // Pure input

.OUT(taper_100ma) , // Noise cuted H signa

.ctl_osc(ctl_osc_taper) // H:Demand clock

) ;

// 一行で書く

ACTIVE_TS ACTIVE_TS_U1(.state(state),.pre_err_ts_inbuff(pre_err_ts_inbuff),.err_ts_inbuff(err_ts_inbuff));

// 呼び素子空呼び出し

UYOBI01_01 YOBI_U1 () ;

UYOBI02_01 YOBI_U2 () ;

UYOBI03_01 YOBI_U3 () ;

endmodule

module ACTIVE_TS(state,pre_err_ts_inbuff,err_ts_inbuff );

input [32:0] state ;

input pre_err_ts_inbuff ;

output err_ts_inbuff ;

wire pre2_err_ts_inbuff ;

// ゲート記述

ND1LU1 ADD1430A ( .A(pre2_err_ts_inbuff) , .X(mid_A14000) );

ND1LU1 ADD1430E ( .A(mid4_A14000) , .X(mid5_A14000) );

RT2LU1 ADD1430Y ( .A1(mid5_A14000) , .A2(pre2_err_ts_inbuff) , .X(err_ts_inbuff) );

// ビット指定の組み合わせ回路

assign pre2_err_ts_inbuff = pre_err_ts_inbuff &

( state[3] |

state[31] |

state[32] |

state[12] );

endmodule

●アサイン文(論理合成でバッファーを発生させる、又は手挿入)

module UOUTBUFF_002 (

out_int,

out

);

output out ;

input out_int ;

assign out = out_int ;

endmodule

●オールウェイズ文の中でケースを使用、SIM様遅延、合成用パラメータ、ビット演算子

// synopsys async_set_reset "x_reset"

always @( posedge total_trigger or negedge x_reset ) begin

if( x_reset == 1'b0 ) begin

#3 state[32:0] <= 33'b000_00000_00000_00000_00000_00000_00001 ;

flag_30min <= 1'b0 ;

flag_ttc <= 1'b0 ;

recharge <= 1'b0 ;

charge_again <= 1'b0 ;

flag_uvlo_bat <= 1'b0 ;

end

else begin

casex({become_33 ,become_32 ,become_31 ,become_30 ,become_29 ,become_28 ,become_27 ,

become_26 ,become_25 ,become_24 ,become_23 ,become_22 ,become_21 ,become_20 ,

become_19 ,become_18 ,become_17 ,become_16 ,become_15 ,become_14 ,become_13 ,

become_12 ,become_11 ,become_10 ,become_09 ,become_08 ,become_07 ,become_06 ,

become_05 ,become_04 ,become_03 ,become_02 ,become_01}) //synopsys parallel_case

33'bxxx_xxxxx_xxxxx_xxxxx_xxxxx_xxxxx_xxxx1 :

begin

#3 state[32:0] <= 33'b000_00000_00000_00000_00000_00000_00001 ;

recharge <= 1'b0 ;

charge_again <= 1'b0 ;

end

//----------<省略>-----------------------------

33'bxxx_xxxxx_xxxxx_xxxx1_xxxxx_xxxxx_xxxxx :

begin

#3 state[32:0] <= 33'b000_00000_00000_00001_00000_00000_00000 ;

flag_30min <= 1'b0 ;

flag_ttc <= 1'b0 ;

recharge <= 1'b0 ;

charge_again<= 1'b0 ;

end

33'bxxx_xxxxx_xxxxx_xxx1x_xxxxx_xxxxx_xxxxx :

begin

#3 state[32:0] <= 33'b000_00000_00000_00010_00000_00000_00000 ;

end

//----------<省略>-----------------------------

33'bx1x_xxxxx_xxxxx_xxxxx_xxxxx_xxxxx_xxxxx :

begin

#3 state[32:0] <= 33'b010_00000_00000_00000_00000_00000_00000 ;

end

33'b1xx_xxxxx_xxxxx_xxxxx_xxxxx_xxxxx_xxxxx :

begin

#3 state[32:0] <= 33'b100_00000_00000_00000_00000_00000_00000 ;

end

default #3 state[32:0] <= 33'b000_00000_00000_00000_00000_00000_00001 ;

endcase

end// if's end

end//always's end

_/_/_/_/_/_/_/_/_/_/_/_/_/_/_/_/_/_/_/_/_/_/_/_/_/

■シミュレーション記述

_/_/_/_/_/_/_/_/_/_/_/_/_/_/_/_/_/_/_/_/_/_/_/_/_/

●ゲートSIM起動

●NC-Verilog起動

・リストで指定

#!/bin/csh -f

rm -rf INCA_libs

ncverilog -f vlist +access+wr

・回路名指定

#!/bin/csh -f

#rm -rf INCA_libs

ncverilog SIM_UCCVSD_REGWATCH_01.v UCCVSD_REGWATCH_01.v +access+wr

# +libext+.v+ \

# -y /home/assplib/CS60ALE/V0.1/logic/veri/xl \

# -y /home/assplib/CS60ALE/V0.1/logic/veri/std \

●トップ(SIMは入出力がない)

// ---------------------------------

//

// Top hierarchy module for test

// Jun.16.2006 Ver 0.01

//

// ---------------------------------

module RTC_SIM;

// R-bus

reg [15:0] RBIN ;

wire [15:0] RBOUT;

reg [1:0] BS ;

reg RBW ;

// パラメータ指定

parameter CLK27MHZ = 20; // About half of 40ns

// 回路呼び出し

RTC_TOP RTC_TOP(

.RBIN(RBIN),

.RBOUT(RBOUT),

.BS(BS),

.RBW(RBW),

);

// -------------

// SELECT 1 BUX

// -------------

initial begin

TEST <= 1'b0;

end

// タスク機能のみ呼び出し

reset;

// タスク直値引渡し呼び出し

rbwrite(16'h04EA,8'hFF);

rbread (16'h04EA);

endmodule

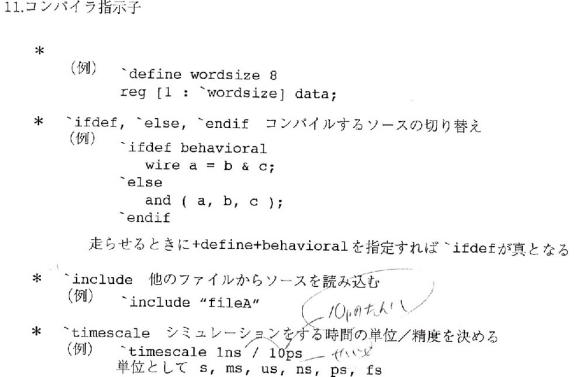

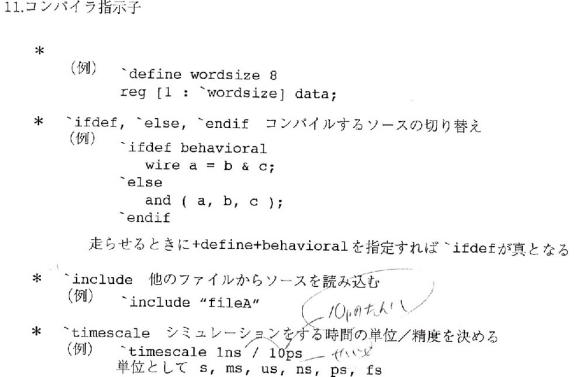

●インクルード

`timescale 1ns/10ps

module SIM_U3DUTYB4_001 ;

`include "../test_common/common.psl"

initial

begin

{b3,b2,b1,b0} = 4'b1001;

#(HALF_CLK*100)

$finish;

end

endmodule

●パラメータ設定

parameter HALF_CLK = 500 ;

●宣言

reg clk;

reg res;

reg b3;

reg b2;

reg b1;

reg b0;

●初期設定

initial

begin

#0clk = 1'b0 ;

#0res = 1'b0 ;

end

●モジュール呼び出し .子(親)

U3DUTYB4_004 X1 (

.b3(b3),

.b2(b2),

.b1(b1),

.b0(b0),

.clk(clk),

.res(res),

.out(out)

);

●クロックとリセットの発生

always #(HALF_CLK)

clk = ~clk ;

initial

begin

res = 1'b0;

@(posedge clk);

@(posedge clk);

#(HALF_CLK/2);

res = 1'b1;

end

●タスクの定義

task yobi_on ;

begin

#(clk_cycle*2*16*300)CTL_CDD1 = 1'b1 ;

if ( i2c_04h_old >= i2c_04h )

check_dac = 1'b0 ;

if ( i2c_04h_old < i2c_04h )

check_dac = 1'b1 ;

#(clk_cycle*2*16*900)CTL_CDD1 = 1'b0 ;

i2c_04h_old = i2c_04h ;

end

endtask

●ファイル出力(起動時)

initial

begin

$dumpfile(create_vcd);

// 0: all node 1: top node

$dumpvars(1, CTL, CK_IN, I2C_04H_D15, I2C_04H_D14, I2C_04H_D13,

I2C_04H_D12, I2C_05H_D15, CTL_CHGSEL, CTL_CDD1, CTL_CDD2,

CS_FINISH, B7, B6, B5, B4, B3, B2, B1, B0 );

end

●スイッチON/OFFで波形出力や遅延解析

initial

begin

//wave file create

`ifdef not_anno

$shm_open(wave_file);

$shm_probe("AS");

`endif

//monitor output

// mon = $fopen(fmon_file) ;

//display output

// dis = $fopen(fdis_file) ;

`ifdef sdf_anno

$shm_open(wave_file_anno); //annotation wave file

$shm_probe("AS");

$sdf_annotate(annotate_file,SIM_U3DUTYB4_001.X1); //set annotation

`endif

//annotate file

// $sdf_annotate(annotate_file,i2c_test.X1.I598); //set annotation

// $sdf_annotate("spx_top.sdf",test_spx_chip_top,,"sdf.log",,"0.6:1.0:1.65",);

end

●データをファイルへ出力

integer fw;

initial

fw = $fopen("temp.ftd");

always @( posedge SIM_U3DUTYB4_001.X1.clk)begin

if(SIM_U3DUTYB4_001.X1.out == 1'b1)

$fdisplay(fw,"P%b%b%b%b%bH",

SIM_U3DUTYB4_001.X1.res,

SIM_U3DUTYB4_001.X1.b3,

SIM_U3DUTYB4_001.X1.b2,

SIM_U3DUTYB4_001.X1.b1,

SIM_U3DUTYB4_001.X1.b0

);

else

$fdisplay(fw,"P%b%b%b%b%bL",

SIM_U3DUTYB4_001.X1.res,

SIM_U3DUTYB4_001.X1.b3,

SIM_U3DUTYB4_001.X1.b2,

SIM_U3DUTYB4_001.X1.b1,

SIM_U3DUTYB4_001.X1.b0

);

end

●簡単に通し,for文、リピート文、各ファイル出力

`timescale 1ns/1ns

module SIM_UDCOUTOP_001 ();

wire [7:0] UDOUT ;

reg [7:0] UDIN ;

// ---------------<省略>-----------------------------------

reg CLK50U;

reg RESET ;

integer temp ;

initial CLK50U = 1'b0;

always #50 CLK50U = ~CLK50U ;

initial begin

RESET = 1'b1 ;

@(posedge CLK50U);

RESET = 1'b0 ;

// for 文

for(temp=255 ; temp >=0 ; temp = temp - 1 )begin

UDIN = temp;

// リピート文

repeat(300) @(posedge CLK50U);

if( UDIN == UDOUT ) $display ("%h=OK",temp); else $display ("%h=NG",temp);

UDIN = 255 - temp;

repeat(300) @(posedge CLK50U);

if( UDIN == UDOUT ) $display ("%h=OK",255-temp); else $display ("%h=NG",255-temp);

end

UDIN = 8'h00;

repeat(256) @(posedge CLK50U);

$finish;

end

//initial #100000 $finish;

UDCOUTOP_001 UDCOUTOP_001(

.UDOUT7(UDOUT[7]),

.UDOUT6(UDOUT[6]),

// ---------------<省略>-----------------------------------

.UDIN1(UDIN[1]),

.UDIN0(UDIN[0]),

.RESET(RESET),

.CLK50U(CLK50U)

);

// ----------

// Make wave

// ----------

initial begin

// For signal scan

//$recordfile("UDCOUTOP_001","sequence");

//$recordvars("trace") ;

//$recordvars("primitives", "drivers") ;

// For IRUN , nc-verilog etc

$shm_open ("UDCOUTOP_001.shm") ;

$shm_probe ( UDCOUTOP_001 , "AS" ) ;

// For vcd

//$dumpvars (1,UDCOUTOP_001) ;

//$dumpfile ("1_1_1.vcd") ;

// For evcd

// $dumpports( UDCOUTOP_001_gate.UDCOUTOP_001,"1_1_1.evcd");

//$dumpports( UDCOUTOP_001,"1_1_1.evcd");

end

initial begin

$sdf_annotate("UDCOUTOP_001.sdf",SIM_UDCOUTOP_001.UDCOUTOP_001); //set annotation

end

endmodule